随着微电子技术、计算机技术、信息技术的不断发展, 继电保护技术也得到了迅速的发展, 从最初的电磁式保护装置发展到如今的集网络化、智能化、保护测控于一体的微机继电保护测控装置, 并且在电力系统中广泛应用[1,2]. 电力系统量测控制设备是构建智能电网的基础, 实现智能电网目标的载体[3], 其能否正常运行直接影响到电力系统运行的可靠性和安全性. CPU板卡作为继电保护测控装置的核心板卡, 其硬件功能的正确性及性能的好坏, 直接关系到装置运行的安全性和可靠性. 在继电保护CPU板卡生产调试阶段, 需要对各功能模块进行测试, 从功能上进行验证及对关键性能指标进行评估[4], 以保证满足设计的要求. 传统的人工测试方法费时费力, 甚至无法达到测试目的, 并且操作繁琐, 重复作业, 容易出错.

在测试过程中引入自动化工具进行自动化测试, 是一种非常实用高效的方法[5–7]. 目前的继电保护自动测试系统主要针对保护测控装置进行设计, 而针对CPU板卡的自动测试开发较少. 为加快生产测试流程, 提高测试效率, 本文设计了一种继电保护CPU板卡的硬件自动测试系统. 该自动测试系统采用模块化、层次化设计, 通用性强, 自动化程度高, 测试过程无需人工干预, 有效避免人工测试过程中漏测测试项、错接测试线等造成的质量隐患, 极大缩短CPU板卡的生产调试周期.

1 CPU板卡模块化分析CPU 板卡是在分析和借鉴了国内外同类产品基础上, 从技术和开发手段的先进性, 软硬件资源的通用性, 系统的可靠性等方面考虑, 开发研制的高性能保护测控插件. 目前本公司CPU板卡主要采用PowerPc架构处理器MPC8377、MPC8313、MPC8309, 以及Xilinx公司的ARM+FPGA组合架构ZYNQ-7000 系列等高性能处理器作为主控制芯片, 构建保护控制自动化系统硬件平台.

综合考虑各类CPU板卡, 按照板上各种硬件资源所实现的功能不同, 可以将CPU板卡资源划分为表1所列功能模块. 本文CPU板卡是对CPU保护插件、通信管理插件等使用高性能处理器作为主控芯片的相关插件统称.

| 表 1 CPU板卡功能模块及描述 |

随着电力系统的不断发展, 电力系统保护自动化装置的功能需求更加多样化, 继电保护CPU板卡的硬件功能模块也会不断发展壮大.

本自动测试系统中所用到的测试方法都是以CPU 板卡的模块化分析为基础的, 根据CPU板卡各种硬件功能模块的特点, 采用不同的测试方法, 实现硬件功能模块的自动化测试, 进行功能验证和性能评估, 并按照功能模块对测试结果进行记录、归档.

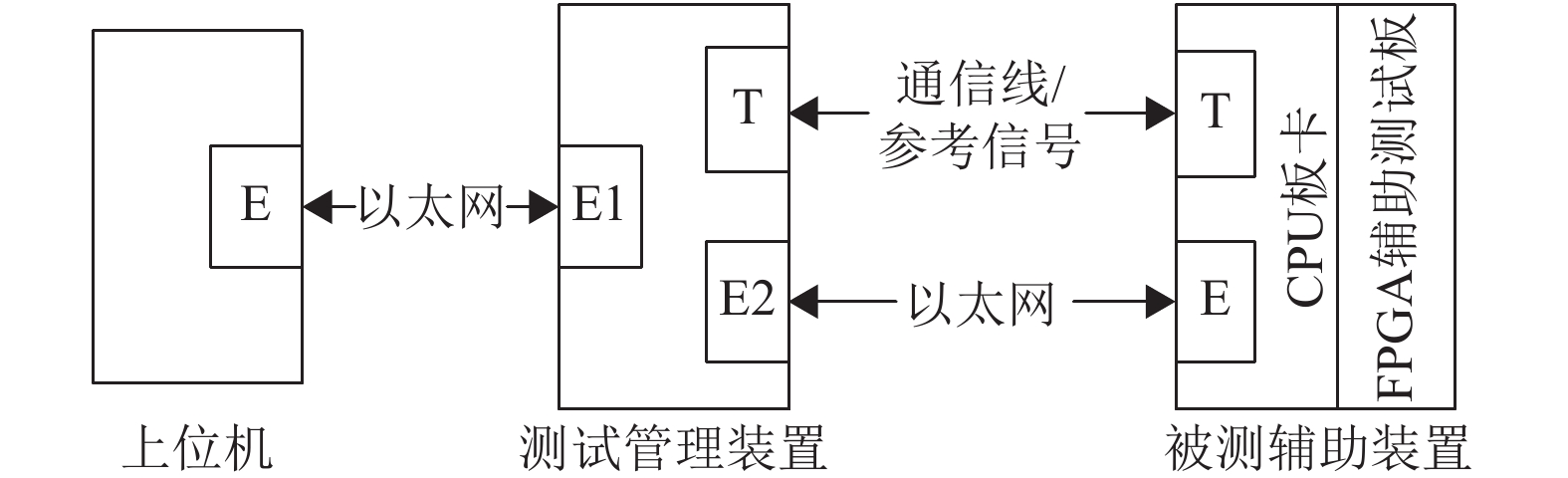

2 自动测试系统设计 2.1 系统总体架构CPU板卡自动测试系统遵循模块化、通用性、实用性、经济性的总体设计原则, 从硬件组成上分为测试管理装置、被测辅助装置、PC上位机等几部分, 其总体架构如图1所示. PC上位机与测试管理装置之间使用以太网通信, 实现测试命令的下发及测试结果的最终上送. 测试管理装置与被测辅助装置内的CPU 被测板卡通过以太网通信, 实现测试交互. 测试管理装置还通过通用异步串口与被测辅助装置内的测试辅助板通信, 下发数模转换命令, 产生AD通道测试所需的模拟量, 施加到CPU 板卡的模拟通道上. 在部分硬件模块(以太网、串口等)测试时, 测试管理装置与CPU板卡之间需要通过相应通道接口进行数据报文收发、产生测试参考信号等.

|

图 1 系统总体架构 |

2.2 测试管理装置

测试管理装置主要由电源插件、核心控制插件、以太网通信插件、以太网转接插件、串口扩展插件、出口扩展插件等部分组成, 各部分通过背板连接. 各插件主要采用公司现有的供货板卡, 只需针对该装置设计专用背板插件, 以节约产品开发成本. 测试管理装置的主要功能包括: 接收上位机发送的测试命令, 向被测CPU板卡转发测试命令; 接收背测板测试结果, 并向上位机转发测试结果; 提供足够的光以太网口、电以太网口、RS232/RS485串口、开出等物理接口, 及其它各类辅助测试资源. 测试管理装置的功能组成框图如图2所示.

|

图 2 测试管理装置功能组成框图 |

为提高整个测试系统的通用性, 测试管理装置的功能资源应按照最大化的要求进行设计, 以满足各类CPU板卡的测试需要. 测试管理装置具体实现以下功能:

(1) 1路电以太网口, 与上位机通信;

(2) 1路电以太网口, 与被测CPU板卡通信;

(3) 1路RS232串口, 与被测辅助装置内辅助测试板卡上的DA 转换模块通信, 发送DA 转换命令;

(4) 8路电以太网口, 用于测试被测CPU板卡的电以太网口;

(5) 8路光以太网口, 用于测试被测CPU板卡的光以太网口;

(6) 3路RS485, 用于测试被测CPU板卡的RS485串口;

(7) 2路RS232, 用于测试被测CPU板卡的RS232串口;

(8) 1路光B码和1路电B码输出, 为被测CPU板卡光B码测试提供参考信号;

(9) 14对出口触点信号, 用于辅助测试被测CPU 板卡的开入通道;

(10) 2路光纤通道, 用于测试被测CPU 板卡的光纤通道.

2.3 被测辅助装置被测辅助装置主要由电源插件、被测CPU 板卡、FPGA辅助测试板卡等几部分组成, 各部分通过背板实现电气信号连接, 其中FPGA辅助测试板卡为新设计插件. 被测辅助装置主要功能包括: 为被测CPU 插件提供供电电源; 在FPGA辅助测试板卡的辅助下完成扩展开入、扩展开出、扩展总线、按键通道、液晶控制信号、IO 信号等硬件功能模块的测试工作.

FPGA辅助测试板为被测辅助装置的重要组成部分, 主要由FPGA可编程逻辑器件、电平转换电路、以太网口转接电路及DA转换模块等组成, 如图3所示.

|

图 3 FPGA辅助测试板组成框图 |

被测CPU板卡所有背板端子引线经背板全部转接至FPGA辅助测试板. 被测板通过背板端子上的总线与FPGA辅助测试板实现信息交互. FPGA可编程逻辑器件通过检测相应背板引线上电平参考信号的变化, 产生测试结果并反馈给被测CPU 板卡; 或主动给相应背板引线输出电平参考信号, 由被测CPU板卡回读该电平参考信号并产生测试结果. 电平转换电路将背板端子的出口、按键等的24V或5V电平转换为3.3V电平信号连接到FPGA可编程逻辑器件. 以太网口转接电路将CPU板卡背板网口引线转接到FPGA辅助测试板前面板上的RJ45端子, 与测试管理装置实现通信, 实现信息交互. DA转换模块主要由微控制器及DA转换芯片组成, 通过前端子的串口接收测试管理装置发送的数据包, 选择并通过相应通道输出电压或电流模拟量.

FPGA辅助测试板的设计使用为扩展开入、扩展开出、扩展总线、按键通道、液晶控制信号、IO 信号等硬件功能模块的测试提供一种高效便捷的测试方法, 不需要借助产品整装置来完成测试, 并且不需要额外的测试设备施加激励, 节约了测试成本.

2.4 上位机测试管理软件PC上位机测试管理软件基于Windows操作系统, 用于CPU板卡测试用例的编辑、测试命令下发及测试信息管理等. PC上位机与测试管理装置使用以太网通信, 通过定时收发心跳报文检测和指示通讯线路通讯状态; 发送测试命令给测试管理装置, 并接收测试管理装置上送的测试结果. 通过TCP与UDP协议对比分析, 在局域以太网上采用UDP进行内部通信比较合适, 根据该系统的应用特点, 传输层协议采用UDP通信协议. UDP 协议不需要建立连接, 响应速度快, 具有较少的流量控制和差错控制, 系统开销比较小[8–10].

软件功能模块结构如图4所示, 主要包括以下功能模块:

|

图 4 PC上位机测试管理软件结构 |

(1) 用户管理: 包括用户登录验证、用户注销、密码设置;

(2) 测试命令下发: 发送启动自动测试命令及中止测试命令;

(3) 测试过程输出展示: 将测试过程及结果分模块展示, 便于掌握测试进度;

(4) 测试报告生成: 将测试结果信息按规定格式保存为PDF文件;

(5) 系统参数设置: 根据设置的参数进行系统设置, 并将参数保存到配置文件中;

(6) 报文监视: 实时查看以太网通信链路上原始报文数据, 便于系统调试;

(7) 通信状态指示: 指示通信链路的工作状态.

测试用例包括具体CPU 板卡型号、硬件功能模块测试项以及各硬件模块相应测试参数设置, 如收发数据包数量、数据包长度、通道数、模拟量值、等待时间等. 采用xml类型的文件编辑存储, 每个硬件功能模块测试项对应其中的一个元素, 元素可以有子元素和属性. 每种不同类型板卡可对测试项目进行勾选并保存下来建立测试用例库, 测试管理软件根据所测试的CPU 板卡型号, 自动选择调用相应测试用例文件, 完成自动测试.

测试管理软件能够将测试过程实时展示出来, 并且在测试完成后, 根据规格要求将测试结果生成PDF文件保存起来, 以便测试人员查看、归档.

3 测试方法及测试流程按照测试方法的不同, 将被测CPU板卡的硬件功能模块分为三大类, 分别为: 装置辅助类、板上自检类和背板引线类.

3.1 装置辅助类功能模块测试装置辅助类硬件功能模块包括以太网口、RS485/RS232串口、B码对时、光纤通道、开入等, 其特点是测试过程需要在测试管理装置的辅助作用下完成. CPU 板卡上该类模块通过与测试管理装置上的相同类型模块收发数据或接收测试管理装置下发的参考信号, 实现对其功能及性能测试评估.

装置辅助类硬件功能模块测试流程为: 如图5所示, 上位机首先通过网口E给测试管理装置网口E1发送测试命令, 测试管理装置通过网口E2将测试命令转发给被测辅助装置中CPU板卡的网口E, CPU板卡接收到测试命令后进入测试模式.

|

图 5 装置辅助类硬件功能模块测试流程示意图 |

下面分两种情况说明:

(1) 当CPU板卡待测模块T为网口、串口等通信接口时, CPU板卡通过T给测试管理装置的T发送数据包, 测试管理装置接收到数据包后对数据包内的方向标志取反后发回给CPU板卡, CPU板卡对定量收发的数据包进行比较统计, 产生测试结果.

(2) 当CPU板卡待测模块T为开入或B码时, 测试管理装置在收到测试命令后, 通过T输出参考信号, CPU板卡待测模块T通过检测该信号状态变化或对该信号进行解码, 判断待测模块的工作状态, 产生测试结果. CPU板卡将测试结果通过网口E反馈给测试管理装置网口E2, 再通过测试管理装置网口E1发送给上位机, 实现对该模块功能及性能测试评估.

3.2 板上自检类功能模块测试板上自检类硬件功能模块主要包括测温模块、实时时钟、电压监测、FLASH、DDR等, CPU板卡上该类模块没有端子引线, 通过自身读写自检测试实现对其功能及性能测试评估.

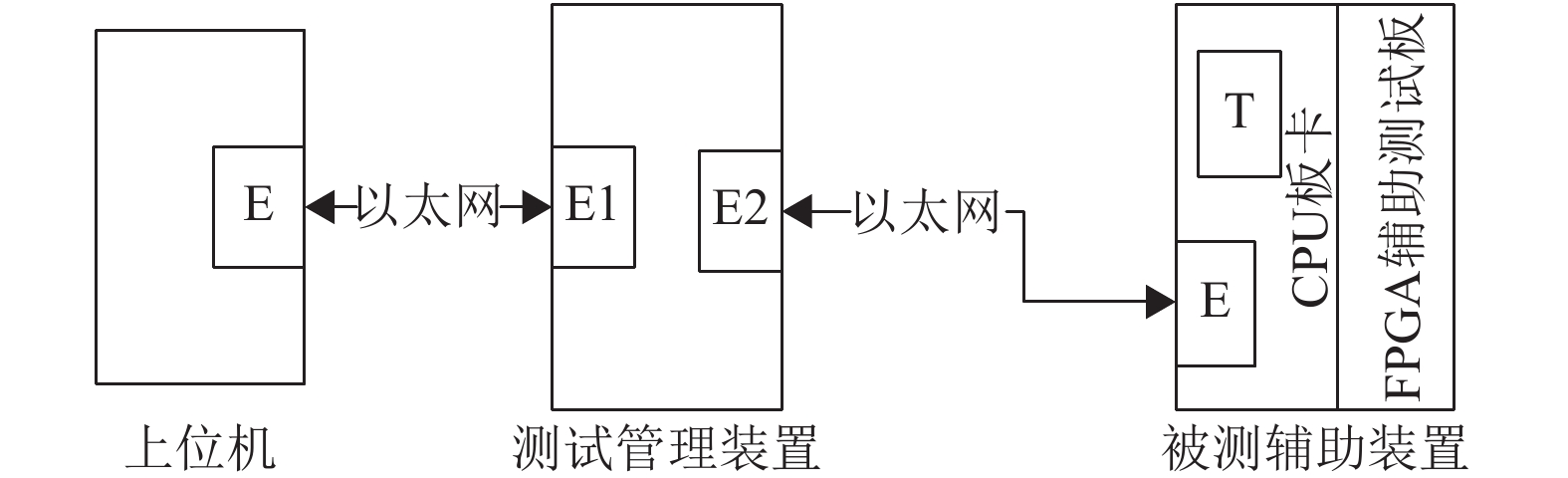

板上自检类硬件功能模块测试流程为: 如图6所示, 板上自检类硬件功能模块测试中, 上位机与测试管理装置之间的通信同装置辅助类硬件功能模块测试过程. 当CPU板卡E网口接收到测试管理装置E2网口转发的测试命令后, 待测硬件模块T进入读写自检测试, 产生测试结果, 实现对该模块功能及性能测试评估.

|

图 6 板上自检类硬件功能模块测试流程示意图 |

3.3 背板引线类功能模块测试

背板引线类硬件功能模块主要包括扩展开入、扩展开出、AD通道、按键通道、液晶控制信号、扩展总线、IO信号等. CPU板卡上该类模块信号经背板端子连接至FPGA辅助测试板, 在FPGA辅助测试板的配合下实现对其功能及性能测试评估.

背板引线类硬件功能模块的测试主要是通过FPGA辅助测试板实现的. 如图7所示, 当CPU板卡E网口接收到测试管理装置E2网口转发的测试命令后, 待测模块T进入测试模式. CPU板卡通过背板总线实现与FPGA辅助测试板交互, 由于不同模块背板引线信号的方向不同, 测试实现中会有所不同.

(1) CPU板卡背板引线信号方向为输出的信号, FPGA辅助测试板接收到相应模块的测试命令后, 进入检测背板连线信号变化工作状态, CPU板卡控制背板连线信号变化, FPGA辅助测试板根据检测情况产生测试结果, 并将结果暂存到FPGA内部寄存器中, 待CPU板卡通过背板总线读取测试结果.

|

图 7 背板引线类硬件功能模块测试流程示意图 |

(2) CPU板卡背板引线信号方向为输入的信号, FPGA辅助测试板接收到相应模块的测试命令后, 控制相应背板连线信号变化, CPU检测信号变化情况, 据此产生测试结果.

(3) AD通道测试时, 测试管理装置通过串口S以固定帧格式发送数字量、AD通道号给FPGA辅助测试板的DA转换模块, DA转换模块将数字量转换为模拟量信号, 并输出给被测CPU板卡相应模拟量通道, CPU读取AD采样值并与测试管理装置通过以太网通信口发送的数字量值进行比较, 据此判断AD采样通道功能是否正常.

FPGA辅助测试板的设计使用, 为背板引线类硬件功能模块的测试提供了高效快捷的测试方法. 下面以扩展总线测试举例说明该类CPU模块测试软件的具体实现. 扩展总线包括片选信号、读写信号、8位数据线、8位地址线, 测试软件流程如图8所示.

|

图 8 扩展总线测试软件流程图 |

(1) CPU板卡通过扩展总线向FPGA辅助测试板0x00地址进行一次写操作, 启动测试;

(2) CPU板卡通过扩展总线依次读地址0x01、0x02、0x04、0x08、0x10、0x20、0x40、0x80;

(3) CPU判断所读数据, 每次读数应为相应地址的反码(FPGA进行逻辑处理), 否则输出异常;

(4) 输出测试结果.

使用该方法能够同时测试到地址线与地址线、数据线与数据线、地址线与数据线、地址线与VCC、数据线与VCC、地址线与GND以及数据线与GND之间是否短路, 数据线、地址线、控制线连接是否正确, 实现了对扩展总线的全面测试.

4 应用实例目前, 该自动测试系统已经应用于MPC8313、MPC8377系列处理器相关的CPU板卡生产过程的测试之中. 以某型号的微机测控装置内的CPU板卡为例, 该CPU板卡上待测硬件功能模块如表2所示.

| 表 2 某型号CPU板卡测试项 |

从表中各功能模块的测试时间来看, 开入、AD通道、以太网、B码对时等几项测试所用时间较多, 而使用FPGA辅助测试板完成的测试项如扩展总线、液晶控制信号、IO信号、按键通道等所用时间较少. 从PC上位机启动测试开始, 到测试完成生成测试报告, 整个测试过程不需人工干预, 该CPU板卡测试时间约为59 s, 与传统人工测试至少30分钟以上测试时间相比, 测试效率大幅提高. 由于各类CPU板卡的板上硬件功能模块的差异, 测试时间会有所不同, 综合分析各类板卡, 其测试时间均在2分钟以内.

5 结论与展望CPU板卡自动测试系统采用模块化、层次化设计, 主要由测试管理装置、被测辅助装置、PC上位机等几部分组成. 根据CPU 板卡上各硬件功能模块的特点, 将其分为三大类, 分别采用不同的测试方法, 实现了CPU板卡硬件功能模块的自动测试, 节省了人力物力成本, 减少测试过程中的人为错误, 极大缩短产品的生产调试周期. 进一步地, 使用工业机器人配合该自动测试系统, 实现测试系统的接线、更换待测CPU板卡、下载测试程序等各工序的自动化作业[11], 提高测试准备等生产测试各个环节的生产效率, 能够更好地发挥自动测试系统的作用.

| [1] |

李响, 刘国伟, 冯亚东, 等. 新一代控制保护系统通用硬件平台设计与应用. 电力系统自动化, 2012, 36(14): 52-55. |

| [2] |

邓丰强, 吕飞鹏, 廖小君, 等. 考虑系统运行方式的继电保护在线智能校核. 电力系统及其自动化学报, 2013, 25(5): 71-76. DOI:10.3969/j.issn.1003-8930.2013.05.014 |

| [3] |

曹军威, 万宇鑫, 涂国煜, 等. 智能电网信息系统体系结构研究. 计算机学报, 2013, 36(1): 143-167. |

| [4] |

琚成, 梁天翼, 贾芸芳. 嵌入式系统中硬件关键性能指标测试模块的设计与实现. 南开大学学报(自然科学版), 2013, 46(5): 50-55. |

| [5] |

王忠, 张晓莉, 李忠安, 等. 继电保护装置自动测试系统设计. 电力系统保护与控制, 2015, 43(5): 130-135. |

| [6] |

应站煌, 胡建斌, 赵瑞东, 等. 继电保护装置自动测试系统研究和设计. 电力系统保护与控制, 2010, 38(17): 142-146. DOI:10.7667/j.issn.1674-3415.2010.17.029 |

| [7] |

李忠安, 沈全荣, 王言国, 等. 电力系统智能装置自动化测试系统的设计. 电力系统自动化, 2009, 33(8): 77-80. DOI:10.3321/j.issn:1000-1026.2009.08.016 |

| [8] |

赵飞, 叶震. UDP协议与TCP协议的对比分析与可靠性改进. 计算机技术与发展, 2006, 16(9): 219-221. DOI:10.3969/j.issn.1673-629X.2006.09.075 |

| [9] |

孙露, 王黎明. 基于UDP/IP协议分布式测试高速数据传输嵌入系统设计. 核电子学与探测技术, 2014, 34(6): 750-753, 779. DOI:10.3969/j.issn.0258-0934.2014.06.018 |

| [10] |

孙振华, 高传发, 张亭, 等. 继电保护硬件平台测试软件一体化设计. 计算机系统应用, 2016, 25(3): 214-219. |

| [11] |

谭民, 王硕. 机器人技术研究进展. 自动化学报, 2013, 39(7): 963-972. |

2018, Vol. 27

2018, Vol. 27