图像处理、机器视觉等技术是当今工程领域的热门课题, 图像传输系统的高速化、网络化已经成为这个方向的一个重要组成部分, 也被视为国内外相关领域的焦点[1]. 随着摄像头硬件性能的提升, 图像的像素量也大幅提高. 图像传输设备的高速化和集成化已经成为主流发展方向.

针对网络数据传输的硬件系统, 现在主流的方案都源自不同的嵌入式平台进行搭建. 各自硬件方案都有各自的优缺点, 而达到速度、效率和移植性三者之间的平衡才是以太网传输系统设计的关键. 千兆以太网传输硬件系统[2–5]主要有:

(1)基于进阶精简指令集机器(Advanced RISC Machines, ARM)的硬件平台. 该平台需要ARM的芯片配上千兆网卡, 运行在Linux系统下. 此硬件平台有使用C语言编程, 易于移植在同类芯片, 指令集兼容性好等优点. 但其缺点也很突出, 因为引入网卡, 所以需要编写驱动文件, 不同网卡驱动不兼容, 维护成本高, 操作复杂.

(2)基于数字信号处理(Digital Signal Processing, DSP)芯片的硬件平台. 对于网络而言, DSP内也有集成的以太网接口芯片. 在编写程序时, 可以调用库文件实现以太网的通信, 所以DSP平台相较ARM平台来说开发更容易. 但是, 该平台软件开发的库文件冗余, 裁剪和自定义难度大, 系统设计灵活性不高. 同时因为DSP采用串行指令流和中断机制, 也产生了系统执行效率不高的问题.

(3)基于现场可编程门阵列(Field Programmable Gate Array, FPGA)的硬件平台. FPGA具有逻辑资源多, 集成度高, 处理速度快, 执行效率高, 编程灵活等特点. 针对网络应用, 常使用FPGA和物理层(Physical Layer, PHY)芯片的这种硬件组合. PHY芯片处于OSI模型的物理层, 是一种与外部信号相连的接口芯片. 主要作用是定义了数据传输所需要的电平标准、时钟基准和数据编码等信息, 并向数据链路层提供接口标准. 该系统不用调用库函数或者使用串行指令, 不需要驱动的编写. 通过分模块编写Verilog代码, 完成介质访问控制层(Media Access Control, MAC)配置和PHY芯片的配置, 相对灵活地实现用户数据报协议/因特网互联协议(User Datagram Protocol/Internet Protocol, UDP/IP)协议.

针对这种非压缩、大数据量的特点, 本文设计了一种基于FPGA硬件数据自定义UDP/IP协议的千兆网络图传系统的解决方案. UDP/IP协议主要用在同步通信或者强调实时性的通信中, 该协议是面向无连接的通信, 所以任何时刻都能发送数据[6–8]. 而且, 因为它处理过程很简单, 所以适合进行高速处理. 利用FPGA的高速性、灵活性、硬件资源丰富等特点, 实现硬件UDP/IP协议栈, 达到高速传输的目的.

1 系统总体框架设计系统选用Xilinx公司XC6SLX45T芯片作为硬件开发平台, 并外接VSC8601芯片、ADV7513芯片和三代双倍数据速率(Double Data Rate 3, DDR3)SDRAM芯片. VSC8601芯片作为千兆以太网的PHY芯片, 用于规定以太网物理层电平标准等. ADV7513芯片作为高清晰度多媒体接口(High Definition Multi-media Interface, HDMI)输出图像信息. DDR3 SDRAM主要用于缓存大量图像信息. 由于DUP/IP协议模块使用125 MHz的时钟, 接收数据和发送数据各使用4根数据线发送DDR数据, 所以传输速度可以达到千兆级别.

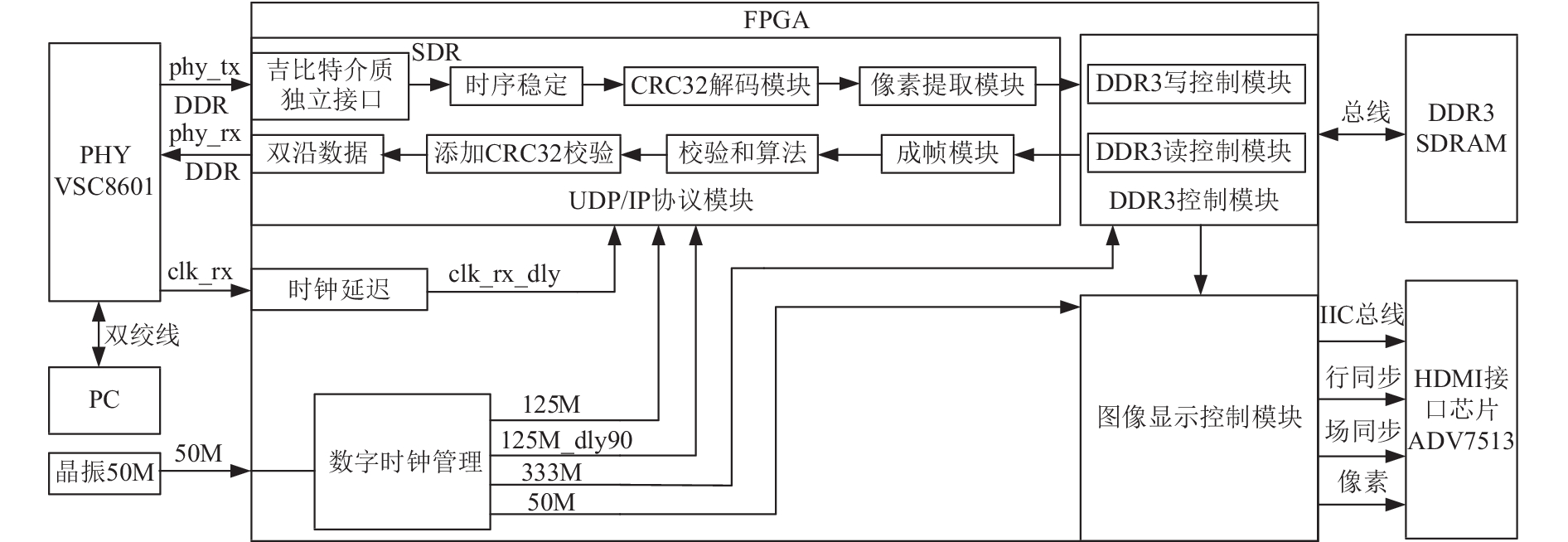

系统设计原理, 如图1所示. PC机将图像信息以UDP协议封装的形式, 通过双绞线发送到以太网PHY芯片. 由于以太网传输数据采用吉比特介质独立接口(Reduced Gigabit Media Independent Interface, RGMII)进行传输数据, 所以FPGA与PHY芯片之间通信, 需要在FPGA端编写双倍数据速率(Double Data Rate, DDR)数据和单倍数据速率(Single Data Rate, SDR)数据之间的转换模块. SDR数据经过UDP/IP协议模块, 将图像信息存入DDR3控制模块. 当一幅图像存储完后, 会产生一个标志信息, UDP/IP协议模块会将图像信息封装起来, 按照UDP/IP协议的格式, 发给PHY芯片. PHY芯片通过双绞线将数据发给PC机. 同时图像显示控制模块也会不停读取DDR3 SDRAM中的图像信息, 通过HDMI接口芯片显示在显示器上.

|

图 1 系统设计原理 |

2 功能模块设计 2.1 UDP/IP协议模块

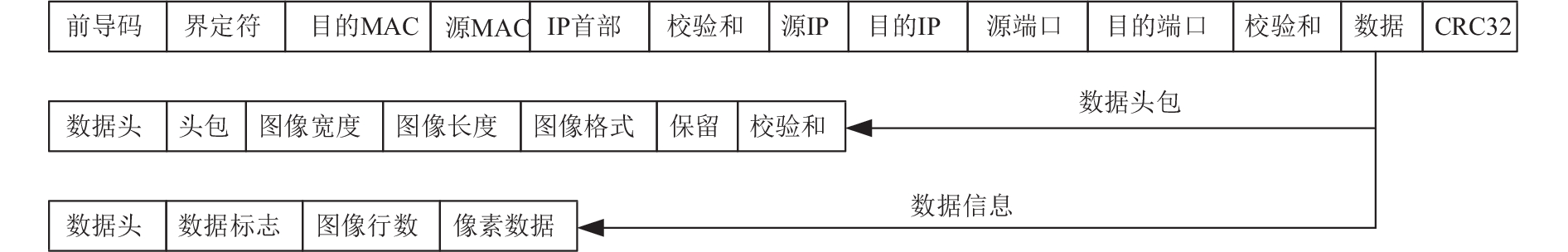

系统根据UDP/IP协议定义以下用于传输图像的UDP/IP协议, 如图2所示. 图中第一行为UDP/IP协议报头格式, 属于国际标准格式[9]. 在UDP/IP数据内容中, 用户可以自定义协议, 用来传输用户的数据, 如图2中第二行和第三行. 发送数据时, 需要先发送一个数据头包, 然后再发送数据信息. 由于UDP协议规定, 每个UDP报文长度不得超过1500个字节, 而一个像素占3个字节, 400个像素即1200个字节. 现定义一个数据包最多携带400个像素信息, 所以传输一幅1024×768个像素的图像的一行(1024个像素点), 需要分3个数据包发送.

|

图 2 UDP/IP协议帧 |

当UDP/IP协议模块接收到图像信息时, 需要先将PHY芯片发来的信息通过时序逻辑, 将数据的时序稳定. PHY芯片的时钟需要经过一个数字时钟管理(Digital Clock Manager, DCM)延迟90度相位, 这样能够提高时钟采集数据的稳定性[10,11]. 将稳定后的数据经过循环冗余校验(Cyclic Redundancy Check 32, CRC32)解码模块后, 通过像素提取模块将像素信息提取出来[12], 将像素信息经过DDR3控制模块写入DDR3. 当一幅图像存储完后, DDR3控制模块会产生一个标志, 成帧模块会将像素打包成UDP协议帧, 在经过校验和算法模块添加校验和, 最后通过CRC32编码生成完整的UDP报文. 此时UDP报文是SDR数据, 需要经过变换成DDR数据发送给PHY芯片, 最后PC机接收到数据, 完成图像传输.

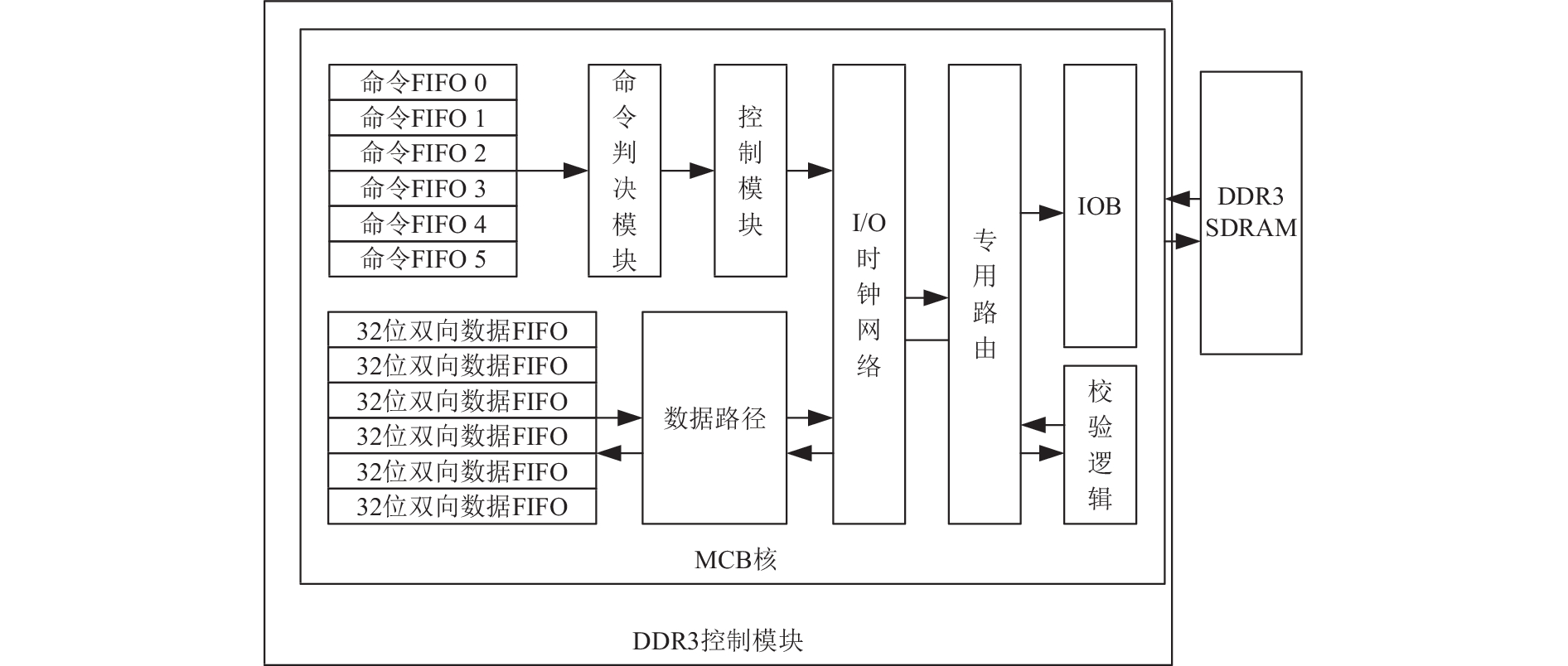

2.2 DDR3控制模块针对DDR3 SDRAM来说, Xilinx公司XC6SLX45T芯片中内置内存控制块(Memory Controller Block, MCB)硬核, MCB是用来控制DDR3 SDRAM. 而用户需要编写一个控制MCB的模块, 实现控制MCB模块, 间接控制DDR3 SDRAM[13,14], 其控制结构如图3所示.

|

图 3 MCB控制模块 |

命令先入先出队列(First Input First Output, FIFO)用于接收DDR3 SDRAM的读写指令, 每当MCB模块接收到读或写指令后, 便会将数据FIFO中的数据读走或写入, 存入或读取DDR3 SDRAM. 控制MCB模块的Modelsim仿真波形如图4所示. MCB模块设置为突发长度为64.

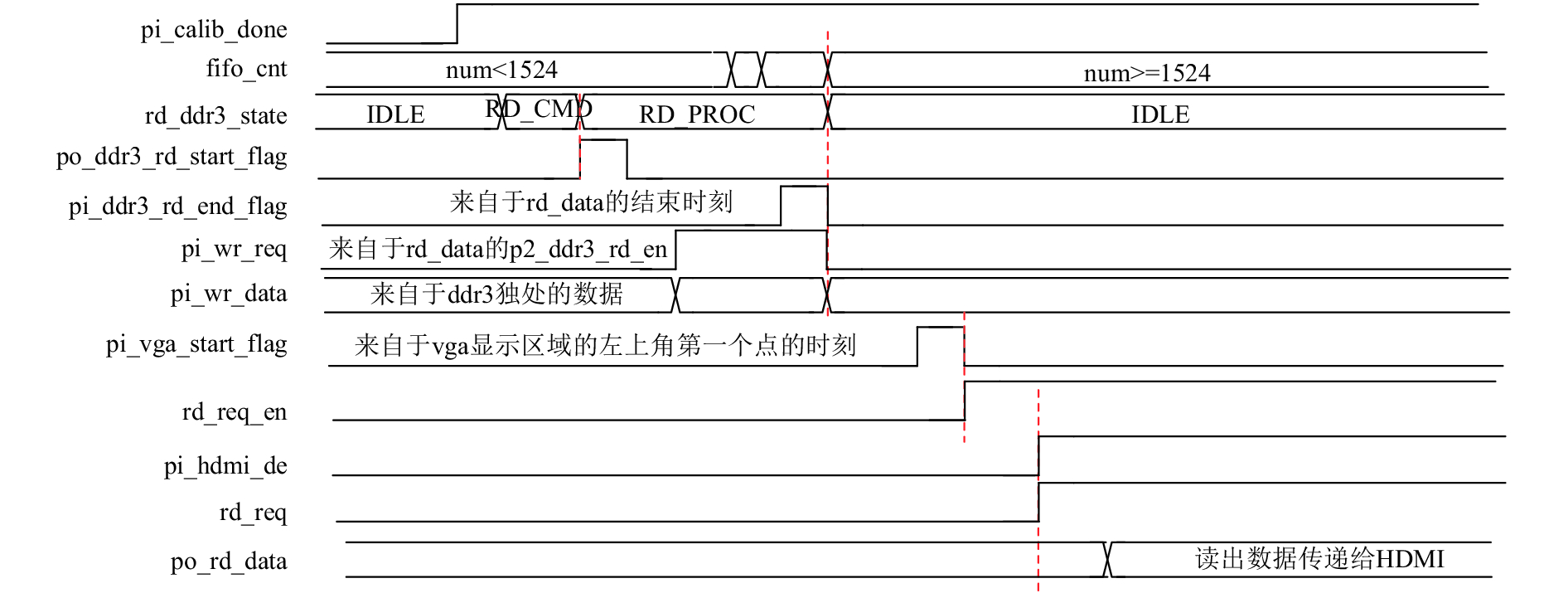

2.3 图像显示控制模块当DDR3 SDRAM芯片上电, 该芯片需要初始化. 之后会产生一个标志信号. 只要该标志信号拉高, 则图像显示模块一直循环从DDR3开始读数据. 由于MCB读出的时钟频率是125 MHz, 而720 P的图像显示时钟频率是65 MHz, 所以需要FIFO进行跨时钟域. 而控制FIFO读数据到HDMI需要设定一个阈值, 实验设定的阈值是1524个数据, 当FIFO内数据超过该阈值则进行读数据到HDMI, 并且MCB只有在FIFO内数据小于该阈值时, 才向FIFO内写数据. 其读写时序如图5.

|

图 4 Modelsim仿真波形 |

|

图 5 图像数据FIFO时序 |

3 系统测试

系统的硬件测试平台如图6所示, 左显示器用于HDMI显示PC机发来的图像, 右显示器用于操作PC机软件, PC端的软件可以显示FPGA发来的图像预览图, 如图7所示. 系统将硬件开发平台用双绞线与计算机直接相连, 先将图像通过PC机发送给FPGA, FPGA收到该图像后, 将图像通过HDMI显示到显示器上, 同时将数据重新打包, 将图像信息以UDP协议封装成数据包, 通过网线发送到计算机上, 计算机收到后, 软件显示收到的图像预览图.

图8是使用Wireshark软件抓取网络数据包, 用该软件可以捕获到FPGA发送给PC机的UDP协议封装的图像数据. 可以从图8中看出, 计算机收到的数据符合UDP/IP协议报文格式, 数据信息为头包+数据包方式传输, 并且一行图像分成了三包数据发送.

图9是使用ChipScope软件抓取的FPGA内部信号的时序图, ChipScope不同于Modelsim仿真软件, 它显示的时序逻辑并不是仿真波形, 而是开发板中的实际波形. 从图9可以看出FPGA发出的数据包格式正确, 硬件系统功能正常.

|

图 6 硬件测试平台 |

|

图 7 PC端图片发送接收软件 |

|

图 8 Wireshark软件抓取的数据 |

|

图 9 ChipScope软件抓取的数据 |

图10是使用Wireshark软件获取的以太网吞吐量, 可以看出传输速度是90124包/s. 一个数据包是1200个字节, 一个字节是8 bit. 经过简单计算可以得到传输速度是865.19 Mbit/s. 由于数据包之间会有包间隔时间, 所以不能真正达到1024 Mbit/s的速度.

4 结论本系统以FPGA和PHY芯片作为硬件平台, 硬件实现UDP/IP协议栈封装图像信息. 系统设计灵活、体积小、速度快, 能够满足高速传输图像的要求. 由于系统MAC层协议是Verilog编程实现, 所以调整方便、成本低、接口简单. 实验测试结果表明, 系统传输数据稳定, 传输速度可达865.19 Mbit/s, 易于维护, 便于移植, 为高清图像传输提供了一种良好的解决方案, 应用前景广泛.

|

图 10 Wireshark抓取的以太网吞吐量 |

| [1] |

俞鹏炜, 任勇, 冯鹏, 等. 基于FPGA的千兆以太网CMOS图像数据传输系统设计. 国外电子测量技术, 2016, 35(11): 76-81. DOI:10.3969/j.issn.1002-8978.2016.11.018 |

| [2] |

付高原, 郭臣, 潘进勇, 等. 基于FPGA的UDP点对点传输协议实现. 电子设计工程, 2017, 25(2): 181-184. |

| [3] |

姜兴家, 刘布民, 何春梅, 等. 一种基于FPGA实现的视频流可靠传输方案. 物联网技术, 2014, 4(2): 44-46. |

| [4] |

王宇聪, 韩启祥, 蔡惠智. 声纳信号处理中UDP协议数据传输研究与设计. 现代电子技术, 2012, 35(1): 78-79, 84. |

| [5] |

侯义合, 张冬冬, 丁雷. 基于FPGA+MAC+PHY的千兆以太网数传系统设计. 科学技术与工程, 2014, 14(19): 275-279. DOI:10.3969/j.issn.1671-1815.2014.19.053 |

| [6] |

顾 颖彦. 反射内存网实时通信技术的研究. 计算机工程, 2002, 28(7): 143-144, 257. |

| [7] |

李勋, 刘文怡. 基于FPGA的以太网接口设计与实现. 自动化与仪表, 2014, 29(5): 57-60. |

| [8] |

肖 卫国, 尔 联洁, 谢 廷毅. 基于共享内存机制微机实时网的数据传输实时性研究. 系统仿真学报, 2004, 16(8): 1717-1720. |

| [9] |

沈潇波, 聂玉鑫. 基于UDP协议的数据桥接单元设计. 声学与电子工程, 2012(1): 27-29. |

| [10] |

Zhao LD. Using UDP datagram to realize a distributed control mode at high-speed data communication. Physics Procedia, 2012(25): 886-891. DOI:10.1016/j.phpro.2012.03.173 |

| [11] |

高富强, 夏禹, 戴正国, 等. 基于UDP的工业CT数据传输系统. 核电子学与探测技术, 2012, 32(3): 311-315, 347. |

| [12] |

陈杰华. 基于FPGA的IP数据报的提取模块的设计. 福建电脑, 2010, 26(2): 125-126. |

| [13] |

范璐, 顾国华, 陈钱. 基于多路UDP的红外图像采集. 数据采集与处理, 2012, 27(S1): 186-189. |

| [14] |

胡冠敏, 徐志军, 许广杰. 基于FPGA的硬件协议栈精简实现. 军事通信技术, 2011, 32(3): 61-65. |

2018, Vol. 27

2018, Vol. 27